Privacy statement: Your privacy is very important to Us. Our company promises not to disclose your personal information to any external company with out your explicit permission.

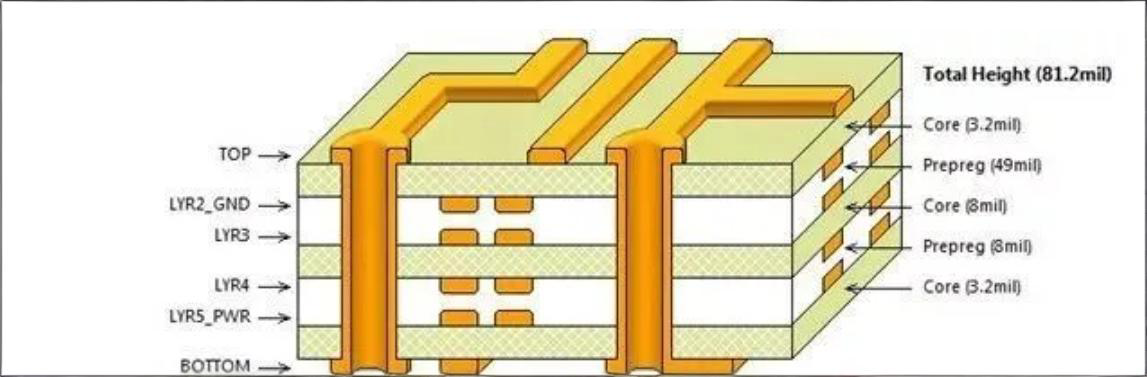

Os circuitos de alta frequência exigem impedância controlada e supressão de ruído. PCBs multicamadas com energia dedicada e planos de aterramento (por exemplo, empilhamentos de 4 ou 6 camadas) reduzem a diafonia em até 50% em comparação com placas de dupla face. De acordo com IPC-2141, uma placa de 4 camadas com espessura dielétrica <0,5 mm pode atingir impedância característica de 50Ω±10%.

Cada milímetro de traço adiciona indutância parasita. Mantenha os sinais de clock e pares diferenciais (por exemplo, USB 3.0) abaixo de 25 mm para evitar EMI. Use a fórmula de reflectometria no domínio do tempo:

T_prop = L√(LC)

Onde L=comprimento do traço, L/C=indutância/capacitância por unidade.

Curvas de 45° ou arco mantêm a continuidade da impedância. As curvaturas em ângulo reto aumentam a capacitância em 20% (conforme IPC-2251), causando reflexão do sinal. Para projetos de 10 GHz+, use traços curvos com raio ≥3×largura do traço.

Cada via introduz capacitância parasita de 0,3–0,5pF (IPC-2221B). Para projetos Ethernet 100G, limite as vias a ≤2 por caminho de sinal. Use microvias (0,1 mm de diâmetro) para placas HDI.

Os traços paralelos devem manter espaçamento ≥3×largura do traço. Para impedância de 50Ω, traços de 0,2 mm requerem folga de 0,6 mm. Coeficiente de acoplamento crosstalk:

K = 1/(1+(D/H)²)

Onde D = espaçamento entre traços, H = altura dielétrica.

Coloque capacitores 100pF – 10nF X7R a 1 mm dos pinos de alimentação do IC. Combine com capacitores em massa de 2,2 μF por IPC-7351B. Isso suprime harmônicos de até 5 GHz.

Use esferas de ferrite (600Ω@100MHz) entre os aterramentos analógico/digital. Mantenha a separação ≥0,5 mm de acordo com IPC-2221. Aterramento de conexão de ponto único próximo a fontes de alimentação.

Mantenha os loops do caminho de retorno <0,01λ na frequência operacional. Para WiFi de 2,4 GHz, a área do loop deve ser <12,5 mm². Use vias de costura de solo a cada λ/10 ao longo de traços críticos.

Calcule a impedância característica usando:

Z₀ = (87/√(ε_r+1,41))×ln(5,98H/(0,8W+T))

Onde ε_r=constante dielétrica, H=altura dielétrica, W=largura do traço, T=espessura do cobre.

Evite saltos de aterramento usando conexões de aterramento com indutância <1nH. Para pacotes BGA, aloque 30% dos pinos para conexões de aterramento conforme IPC-7093.

A implementação dessas técnicas requer fabricação de precisão. Consulte fornecedores experientes de PCB para roteamento controlado por impedância e produção em massa confiável. Solicite orçamentos instantâneos para placas RF multicamadas com espessura de cobre de 1 onça e materiais Rogers.

*Referências de dados: padrões IPC-2221B, IPC-2141A, JESD51-12*

Enviar e-mail para este fornecedor

Privacy statement: Your privacy is very important to Us. Our company promises not to disclose your personal information to any external company with out your explicit permission.

Fill in more information so that we can get in touch with you faster

Privacy statement: Your privacy is very important to Us. Our company promises not to disclose your personal information to any external company with out your explicit permission.